Researchers at MIT and Texas Instruments have unveiled a new chip design for portable electronics that can be up to 10 times more energy-efficient than present technology. The design could lead to cell phones, implantable medical devices and sensors that last far longer when running from a battery.

The innovative design is being presented Feb. 5 at the International Solid-State Circuits Conference in San Francisco by Joyce Kwong, a graduate student in MIT's Department of Electrical Engineering and Computer Science (EECS).

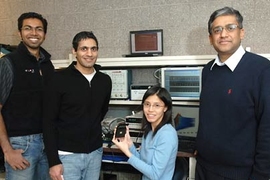

Kwong carried out the project with MIT colleagues Anantha Chandrakasan, the Joseph F. and Nancy P. Keithley Professor of Electrical Engineering, and EECS graduate students Yogesh Ramadass and Naveen Verma. Their Texas Instruments (TI) collaborators are Markus Koesler, Korbinian Huber and Hans Moormann. The team demonstrated the ultra-low-power design techniques on TI's MSP430, a widely used microcontroller. The work was conducted at the MIT Microsystems Technology Laboratories, which Chandrakasan directs.

The key to the improvement in energy efficiency was to find ways of making the circuits on the chip work at a voltage level much lower than usual, Chandrakasan explains. While most current chips operate at around one volt, the new design works at just 0.3 volts.

Reducing the operating voltage, however, is not as simple as it might sound, because existing microchips have been optimized for many years to operate at the higher standard-voltage level. "Memory and logic circuits have to be redesigned to operate at very low power supply voltages," Chandrakasan says.

One key to the new design, he says, was to build a high-efficiency DC-to-DC converter--which reduces the voltage to the lower level--right on the same chip, reducing the number of separate components. The redesigned memory and logic, along with the DC-to-DC converter, are all integrated to realize a complete system-on-a-chip solution.

One of the biggest problems the team had to overcome was the variability that occurs in typical chip manufacturing. At lower voltage levels, variations and imperfections in the silicon chip become more problematic. "Designing the chip to minimize its vulnerability to such variations is a big part of our strategy," Chandrakasan says.

So far the new chip is a proof of concept. Commercial applications could become available "in five years, maybe even sooner, in a number of exciting areas," Chandrakasan says. For example, portable and implantable medical devices, portable communications devices and networking devices could be based on such chips, and thus have greatly increased operating times. There may also be a variety of military applications in the production of tiny, self-contained sensor networks that could be dispersed in a battlefield.

In some applications, such as implantable medical devices, the goal is to make the power requirements so low that they could be powered by "ambient energy," Chandrakasan says--using the body's own heat or movement to provide all the needed power. In addition, the technology could be suitable for body area networks or wirelessly enabled body sensor networks.

"Together, TI and MIT have pioneered many advances that lower power in electronic devices, and we are proud to be part of this revolutionary, world-class university research," said Dr. Dennis Buss, chief scientist at Texas Instruments. "These design techniques show great potential for TI's future low-power integrated circuit products and applications including wireless terminals, battery-operated instrumentation, sensor networks and medical electronics."

The research was funded in part by a grant from the U.S. Defense Advanced Research Projects Agency.

A version of this article appeared in MIT Tech Talk on February 6, 2008 (download PDF).